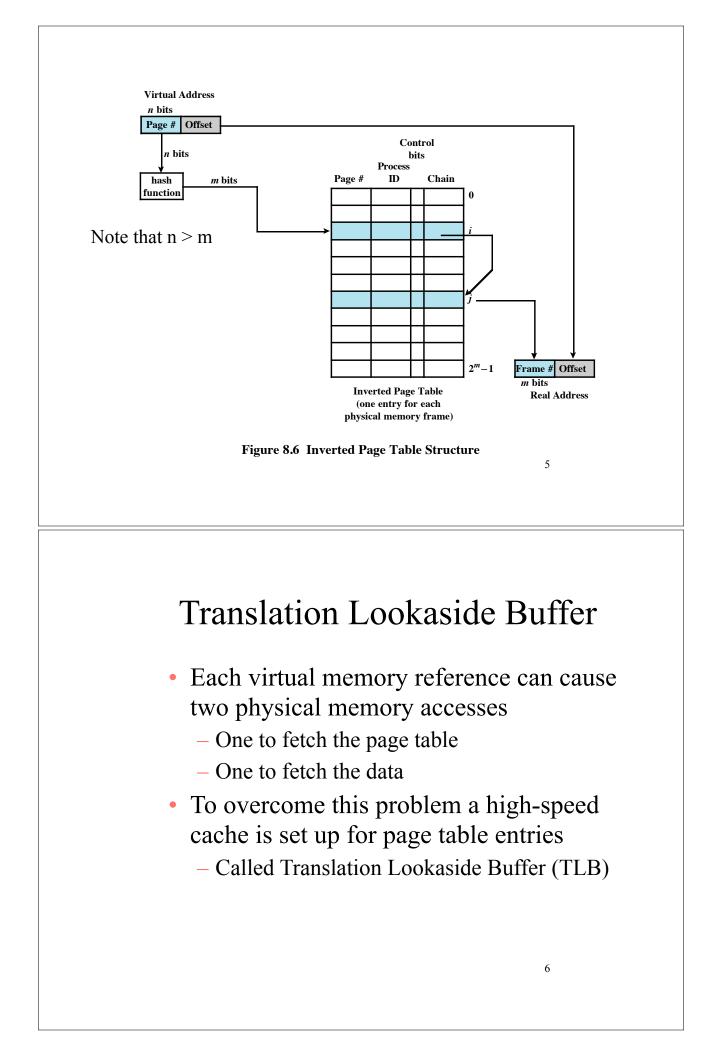

# Inverted Page Table

- Alternative to (multi-level) page table

- Used on PowerPC, UltraSPARC, and IA-64 architecture

- One entry in table for each physical memory frame

- Page number portion of a virtual address is mapped to a hash value

- Fixed proportion of real memory is required for the tables regardless of the number of processes

3

4

### Inverted Page Table

- Page table entries:

- Page number

- Process identifier

- Control bits

- Chain pointer

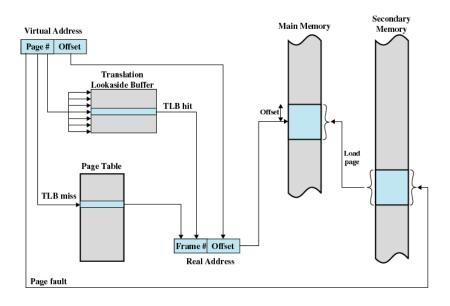

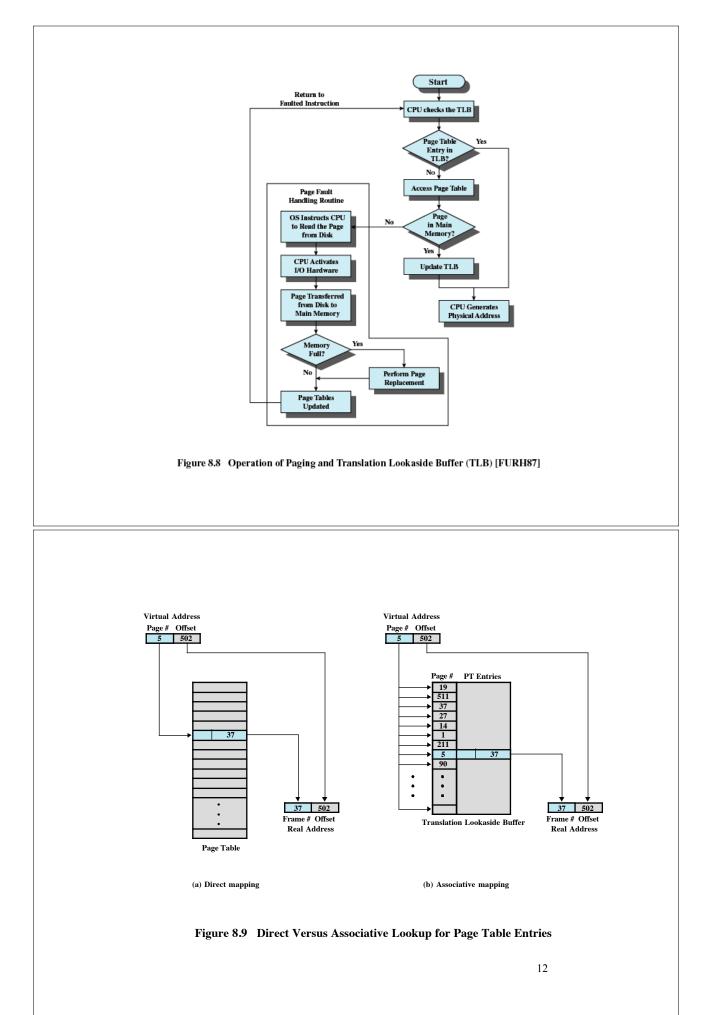

# Translation Lookaside Buffer

• Contains page table entries that have been most recently used

#### Translation Lookaside Buffer

- Given a virtual address, processor examines the TLB

- If page table entry is present (TLB hit), the frame number is retrieved and the real address is formed

- If page table entry is not found in the TLB (TLB miss), the page number is used to index the process page table

7

#### Translation Lookaside Buffer

- First checks if page is already in main memory

- If not in main memory a page fault is issued

- The TLB is updated to include the new page entry

Figure 8.7 Use of a Translation Lookaside Buffer

9

# **Example Page Sizes**

#### Table 8.2 Example Page Sizes

| Computer               | Page Size              |

|------------------------|------------------------|

| Atlas                  | 512 48-bit words       |

| Honeywell-Multics      | 1024 36-bit word       |

| IBM 370/XA and 370/ESA | 4 Kbytes               |

| VAX family             | 512 bytes              |

| IBM AS/400             | 512 bytes              |

| DEC Alpha              | 8 Kbytes               |

| MIPS                   | 4 kbyes to 16 Mbytes   |

| UltraSPARC             | 8 Kbytes to 4 Mbytes   |

| Pentium                | 4 Kbytes or 4 Mbytes   |

| PowerPc                | 4 Kbytes               |

| Itanium                | 4 Kbytes to 256 Mbytes |

17